# **AGENDA**

- PTP Clock Recovery methods

- Oscillator characteristics

- Clock recovery validation parameters

- A model for validation of clock recovery system with oscillator simulation.

- Advantages of oscillator simulated testing

PTP Clock recovery methods

#### PTP CLOCK RECOVERY COMPONENTS

- Clock recovery systems typically comprise of the following

- Oscillator

- DPLLs

- Jitter attenuators, APLLs

- PTP Servo (s/w)

- PTP stack and other control s/w is not considered integral to the actual clock recovery.

#### PTP CLOCK RECOVERY BASICS

- Two way time transfer capable of achieving

- 1usec 10uses in PTP unaware transport

- 100 ns in PTP aware network

- T1, T4 from PTP master

- T2, T3 from PTP client

- Delay = ((T2-T1) + (T4-T3))/2

- Offset = ((T2-T1) (T4-T3))/2

- Noise due to PDV/asymmetry is filtered out by packet selection & filtering, and controlling the loop bandwidth of the PLL

PTP Implementations

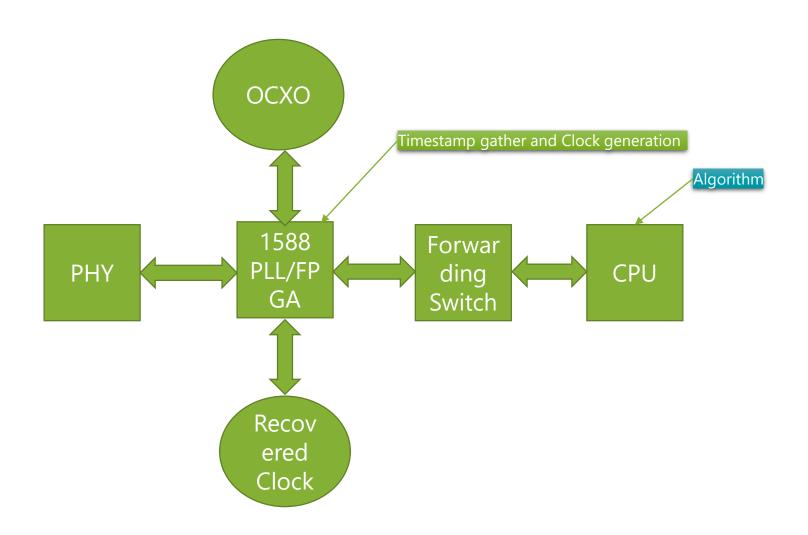

## CENTRALIZED/ALL IN ONE

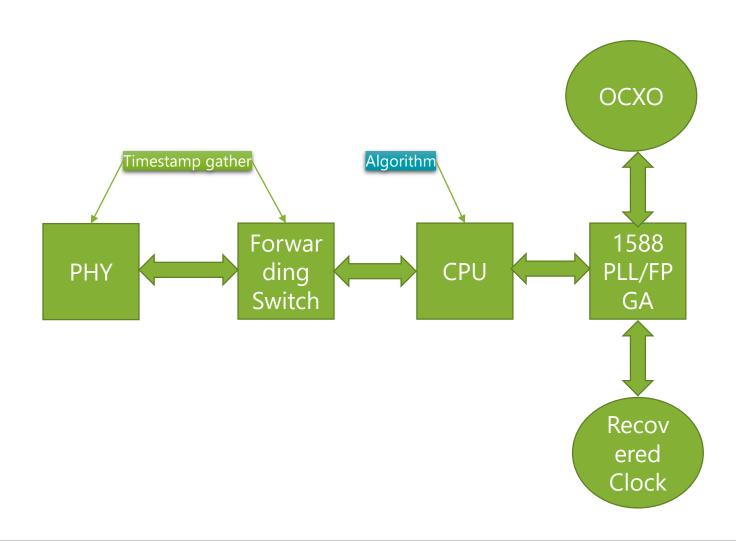

## DISCRETE CLOCK RECOVERY

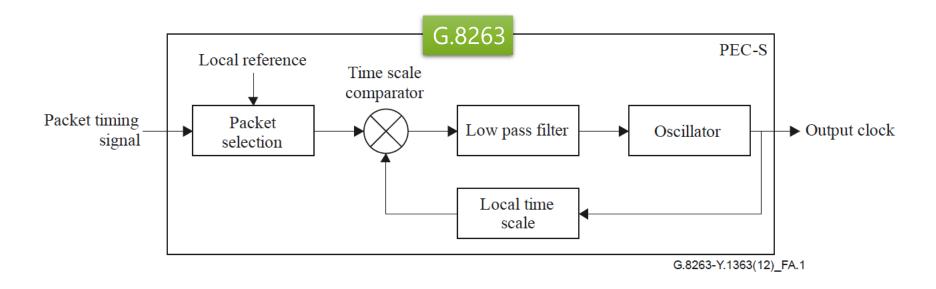

#### STANDARD DEFINED PTP MODEL

Figure A.1 – Functional model of a packet-based equipment clock – slave – frequency (PEC-S-F)

**Oscillator Characteristics**

#### OSCILLATOR CHARACTERISTICS

- Regardless of the PTP clock recovery system design, an oscillator is used as the system clock for the clock recovery solution

- The choice of oscillator depends on the performance requirements of the PTP PLL and the loop bandwidth of the PTP

- The oscillator performance, both deterministic and non-deterministic will determine if the clocking solution would be able to meet the performance requirement (MTIE, TDEV) of the synchronization standard.

- Deterministic factors are oscillator aging, and temperature stability

- Non-deterministic factors are environment factor, and noise (stochastic) of the oscillator.

Clock recovery validation

## PTP SOLUTION EVALUATION WITH OSCILLATOR H/W

- Typically done by testing the actual oscillator hardware with the PLL closed loop.

- Require control and manipulation of the following factors

- Temperature

- Airflow

- Vibration

- But don't have any control on the following factors

- Oscillator noise,

- Short term frequency jumps/instability

A model for validation of clock recovery system with oscillator simulation.

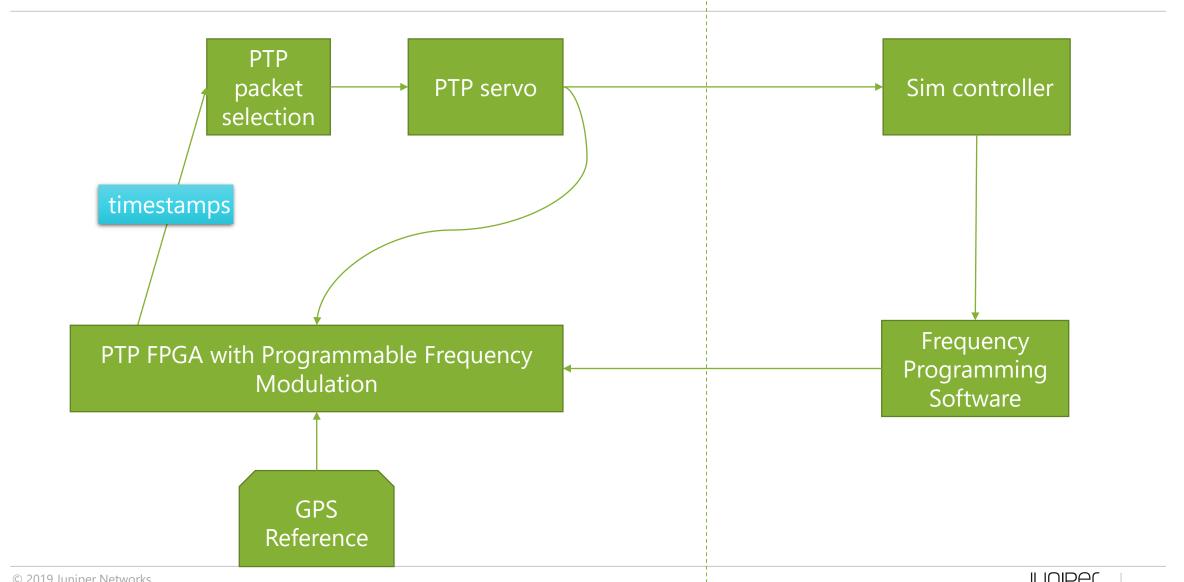

### SIMULATION DESIGN

Advantages of oscillator simulated testing

#### EVALUATION OF THE PTP SOLUTION WITH OSCILLATOR SIMULATION

- Better control on the evaluation of the performance

- Test non-standard and indeterministic behavior of the oscillator

- Test along with packet clock HRM model and network PDVs.

- Able to catch corner case unlocking behavior of the PTP servo

- Able to test holdover performance

- Faster turnaround time for servo algorithm trials.