# Timing in Packet Networks

WSTS 2018 San Jose, 18-21 June 2018

Stefano Ruffini, Ericsson

- -Background

- -Frequency Sync over the Physical Layer

- -Frequency sync via packets

- —Two-Way Time Transfer

- —Time Protocols: NTP/PTP Details

- —Impairments when delivering timing via packets

- —Packet-based Metrics for frequency and time

- Note: some of this material is based on earlier presentations from Christian Farrow and Kishan Shenoi

| _ |     |

|---|-----|

| = | =√i |

|   |     |

|   |     |

# Background

- Packet switching network does not require sync itself (at least traditional packet networks)

- -CBR (Constant Bit Rate) services over ATM, early packet-sync related example

- —Generalization due to **migration to packet networks** (Ethernet-IP; Ethernet Physical layer traditionally defined as «asynchronous»):

- -Current main focus is to deliver **time/phase sync** reference

- Packet-based sync technologies required (may be combined with synchronous physical layer)

- —«Deterministic» packet networks (e.g. **TSN**-IEEE, **Detnet**-IETF) as a related topic

# SyncE: Introduction

- Several applications requiring accurate frequency are reached by Ethernet

- It was agreed to define a synchronous Ethernet physical layer; Not in contradiction with IEEE

- Only in full duplex mode (continuous signal required)

- **Based on SDH** specification (for interoperability and simplifying the standardization task)

- Synchronous Ethernet equipment equipped with a synchronous Ethernet Equipment Clock – EEC (G.8262). Synchronous Ethernet interfaces extract the received clock and pass it to the system clock.

- Synchronization Status Message as per G.8264

- Ongoing work to define an **enhanced SyncE** (G.8262.1)

- Extension to OTN («OEC»):

- G.8262: *Timing characteristics of synchronous Ethernet equipment slave clock*

- It does not transport Time

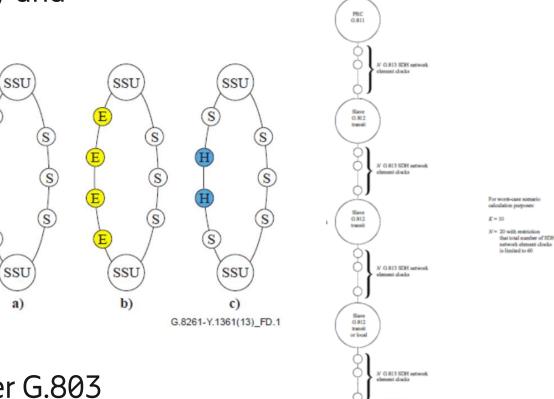

- All nodes must support SyncE: sync chain as per G.803

- Cannot be transported transparently across network boundaries

Figure 8-5/G.803 - Synchronization network reference chain

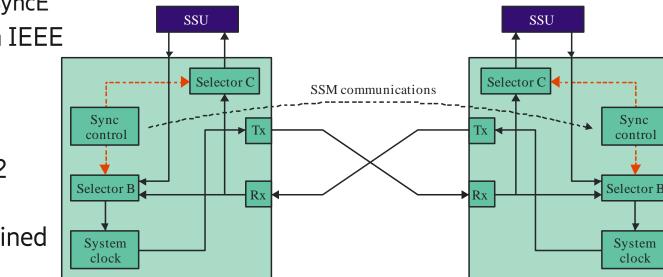

# SSM (Synchronization Status Message) in SyncE

- SSM required to prevent timing loops and to support reference selection (as per SDH)

- Details according to G.781 and G.8264

- In SDH SSM delivered in fixed locations of the SDH frame

- Packet based mechanism required in case of SyncE

- OUI (organizationally unique identifier) from IEEE reused to specify exchange of QLs over the OAM specific slow protocol (OSSP)

- EEC option 1 clock treated as G.813

option 1 (QL-SEC), EEC option 2 as an G.812

type IV clock (QL-ST3).

- Two types of protocol message types are defined

- "heart-beat" message (once per second)

- Event message generated immediately

WSTS 2018 | Public | © Ericsson AB 2018 | 2018-05-30 | Page 5 (54)

- SSM QL value is considered failed if no SSM messages are received after a five second period.

G.8264-Y.1364(14)\_F11-1

# Ethernet synchronization messaging channel (ESMC) Format

- ESMC PDU with QL TLV always sent as the first TLV in the Data and padding field

| Octet number          | Size/bits              | Field                                                        |            |                         |                                         |                                        |

|-----------------------|------------------------|--------------------------------------------------------------|------------|-------------------------|-----------------------------------------|----------------------------------------|

| 1-6                   | 6 octets               | Destination Address = $01-80-C2-00-00-02$ (hex)              |            |                         |                                         |                                        |

| 7-12                  | 6 octets               | Source Address                                               |            |                         |                                         |                                        |

| 13-14                 | 2 octets               | Slow Protocol Ethertype = 88-09 (hex)                        |            |                         |                                         |                                        |

| 15                    | 1 octet                | Slow Protocol Subtype = $0A$ (hex)                           |            |                         |                                         |                                        |

| 16-18                 | 3 octets               | ITU-OUI = 00-19-A7 (hex)                                     | 1          |                         |                                         |                                        |

| 19-20                 | 2 octets               | ITU Subtype                                                  | Oc         | tet number              | Size/bits                               | Field                                  |

| 21                    | bits 7:4 (Note 1)      | Version                                                      |            | 1                       | 8 bits                                  | Type: 0x01                             |

|                       | bit 3                  | Event flag                                                   |            | 2-3                     | 16 bits                                 | Length: 00-04                          |

|                       | bits 2:0 (Note 2)      | Reserved                                                     |            |                         |                                         |                                        |

| 22-24                 | 3 octets               | Reserved                                                     |            | 4                       | bits 7:4 (Note)                         | 0x0 (unused)                           |

| 25-1532               | 36-1490 octets         | Data and padding (See point j)                               |            | $\subset$               | bits 3:0                                | SSM code                               |

| Last 4                | 4 octets               | FCS                                                          | NOTE – Bit | 7 of octet 4 is the mos | st significant bit. The least significa | nt nibble bit 3 to bit 0 (bits $3.0$ ) |

| number for the ESI    | MC.                    | it of octet 21. Bit 7 to bit 4 (bits 7:4) represent the four |            | four-bit SSM code.      | a significant on. The least significa   |                                        |

| NOTE $2 - $ The three | ee LSBs (bits 2:0) are | reserved.                                                    | J          |                         |                                         |                                        |

### - Recently extended to carry new clock types (and inform on PRTC traceability)

Extended QL TLV

— Use of Padding bits also recently revised (set to all zero and ignored by receivers)

| Octet number                                                           | Size/bits                       | Field                                                           |                       | <b>_</b>                              |                                                |                            |

|------------------------------------------------------------------------|---------------------------------|-----------------------------------------------------------------|-----------------------|---------------------------------------|------------------------------------------------|----------------------------|

| 1                                                                      | 8 bits                          | Type: 0x02                                                      |                       | ⊢x†                                   | ended                                          |                            |

| 2-3                                                                    | 16 bits                         | Length: 0x0014                                                  |                       |                                       |                                                |                            |

| 4                                                                      | 8 bits                          | Enhanced SSM code (see Tak<br>6)                                | ole 11-               | QL                                    | TLV                                            |                            |

| 5-12                                                                   | 64 bits                         | SyncE clockIdentity of the originator of the extend TLV, Note1, |                       | · · · · · · · · · · · · · · · · · · · | SyncE clock                                    | Identity<br>EEE 1588 rules |

| 13                                                                     | 8 bits                          | Flag; Note2                                                     |                       |                                       |                                                |                            |

| 14                                                                     | 8 bits                          | Number of cascaded eEECs<br>the nearest SSU/PRC/                |                       |                                       |                                                |                            |

| 15                                                                     | 8 bits                          | Number of cascaded EECs<br>the nearest SSU/PRC/                 |                       |                                       |                                                |                            |

| 16-20                                                                  | 40 bits                         | Reserved for future use                                         | 9                     | Clock                                 | Quality level                                  | Enhanced SSM code          |

|                                                                        |                                 |                                                                 |                       | EEC1                                  | QL-EEC1                                        | 0xFF                       |

|                                                                        |                                 |                                                                 |                       | EEC2<br>r clock types<br>ontained     | QL-EEC2<br>QL message<br>(refer to the QL TLV) | 0xFF<br>0xFF               |

| Note: ePRC SSM code (0x23) recently added (G.8264 Amd1, February 2018) |                                 | in [I                                                           | TU-T G.781]<br>Note 1 | Note 1                                |                                                |                            |

| (G.0204 A                                                              | mui, rebiual                    | y 2010j                                                         |                       | PRTC                                  | QL-PRTC                                        | 0x20                       |

|                                                                        |                                 |                                                                 |                       | ePRTC                                 | QL-ePRTC                                       | 0x21                       |

|                                                                        |                                 |                                                                 |                       | eEEC                                  | QL-eEEC                                        | 0x22                       |

|                                                                        |                                 |                                                                 | Note 1.               | ePRC                                  | QL-ePRC                                        | 0x23                       |

| WSTS 2018   Public   0                                                 | © Ericsson AB 2018   2018-05-30 | Page 7 (54)                                                     | Note 1:<br>T G.781]   |                                       | 11-9 illustrate the full set o                 | T CIOCK Types from [110-   |

# SSM codes for SyncE

#### Table 11-7 (G.8264-2017): Option I

| Clock  | Quality level | SSM code | Enhanced SSM |

|--------|---------------|----------|--------------|

|        |               |          | code         |

| PRC    | QL-PRC        | 0010     | 0xFF         |

| SSU-A  | QL-SSU-A      | 0100     | 0xFF         |

| SSU-B  | QL-SSU-B      | 1000     | 0xFF         |

| EEC1   | QL-EEC1       | 1011     | 0xFF         |

| Note 1 | QL-DNU        | 1111     | 0xFF         |

| PRTC   | QL-PRTC       | 0010     | 0x20         |

| ePRTC  | QL-ePRTC      | 0010     | 0x21         |

| eEEC   | QL-eEEC       | 1011     | 0x22         |

| ePRC   | QL-ePRC       | 0010     | 0x23         |

Note 1: There is no clock corresponding to this quality level.

Note 2: When processing the SSM QL, The SSM code should be processed first, followed by processing the Enhanced SSM code.

If a clock supports both the QL TLV and the extended QL TLV, it should set the SSM code and the enhanced SSM code according to table 11-7/11-8, and send both the QL TLV and the extended QL TLV.

#### Table 11-8 (G.8264-2017): Option II

| Clock  | Quality level | SSM code | Enhanced SSM |  |

|--------|---------------|----------|--------------|--|

|        |               |          | code         |  |

| PRS    | QL-PRS        | 0001     | 0xFF         |  |

| Note 1 | QL-STU        | 0000     | 0xFF         |  |

| ST2    | QL-ST2        | 0111     | 0xFF         |  |

| TNC    | QL-TNC        | 0100     | 0xFF         |  |

| ST3E   | QL-ST3E       | 1101     | 0xFF         |  |

| ST3    | QL-ST3        | 1010     | 0xFF         |  |

| EEC2   | QL-EEC2       | 1010     | 0xFF         |  |

| Note 1 | QL-PROV       | 1110     | 0xFF         |  |

| Note 1 | QL-DUS        | 1111     | 0xFF         |  |

| PRTC   | QL-PRTC       | 0001     | 0x20         |  |

| ePRTC  | QL-ePRTC      | 0001     | 0x21         |  |

| eEEC   | QL-eEEC       | 1010     | 0x22         |  |

| ePRC   | QL-ePRC       | 0001     | 0x23         |  |

|        | • • • • • • • |          |              |  |

Note 1: There is no clock that corresponds to this quality level. Note 2: When processing the SSM QL, The SSM code should be processed first, followed by processing the Enhanced SSM code.

Note: ePRC SSM code (0x23) recently added (G.8264 Amd1, February 2018)

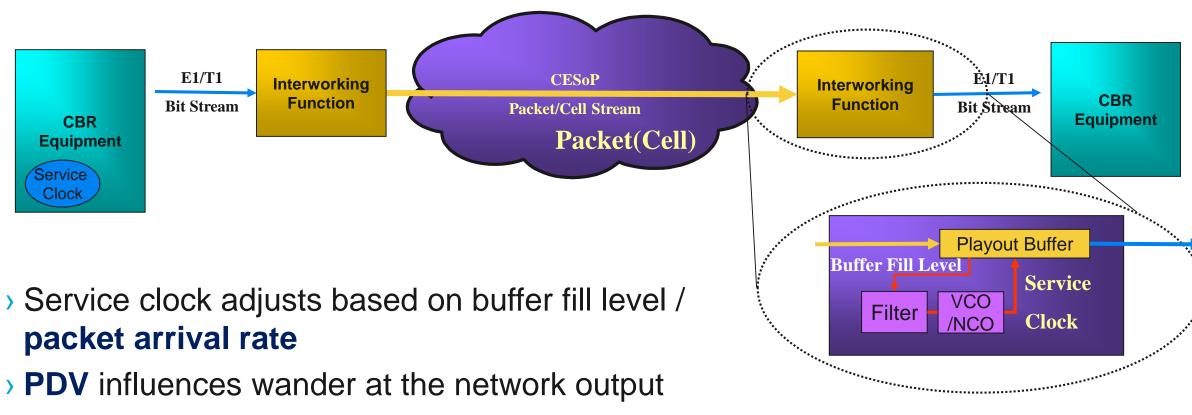

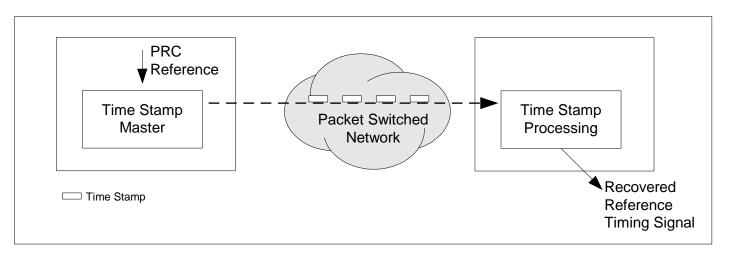

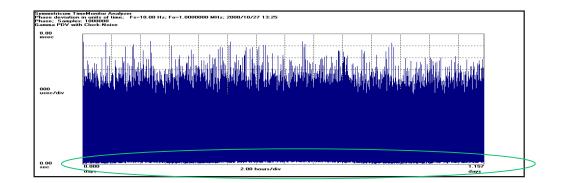

### Packet-Based Timing: Adaptive Clock Operation

> PDV influences wander at the network output

# From clocks to "packet Clocks"

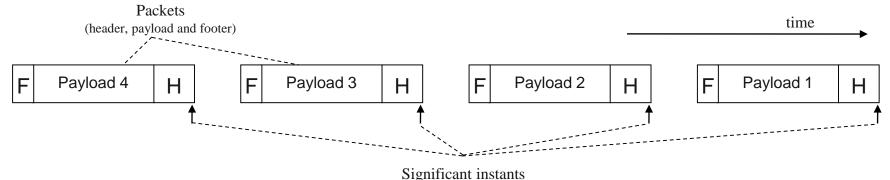

- -CES Packets do have a regular rhythm

- -Extension to using dedicated protocols: NTP, PTP

- Packets may not arrive regularly, but **timestamps** mean time information can be extracted

- Timing information contained in the arrival/departure time of the packets

- Two-way or one-way protocols

- Timing recovery process requires **PDV filtering**

- -Time and frequency can be distributed from point A to point B

### Packet-Based Methods

From ITU-T Recc. G.8261

> Timing information carried by **dedicated timing packets**:

- -Network Time Protocol (NTP) IETF RFC 5905

- -Precision Time Protocol (PTP) IEEE1588-2008

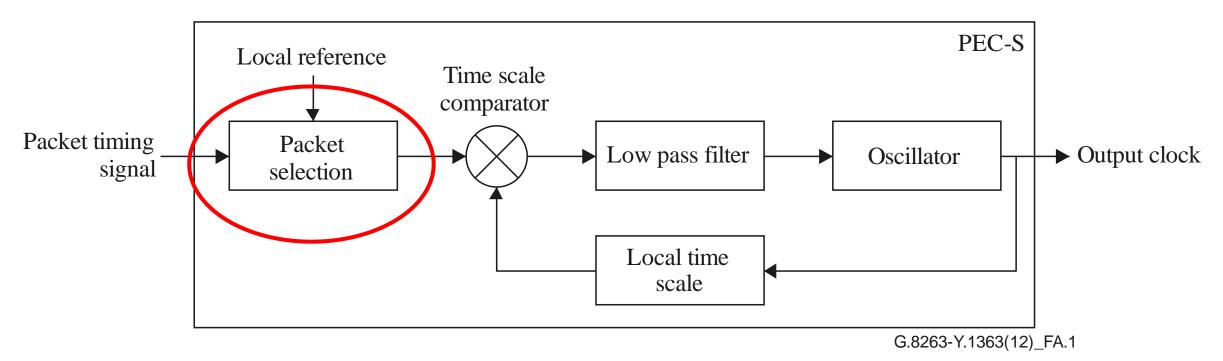

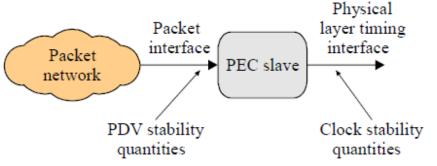

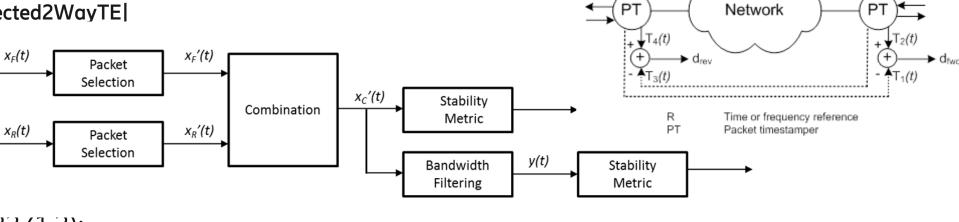

# Packet-based Equipment Clock

-Concept of «**Packet Selection**»:

- Pre-processing of packets before use in a traditional clock to handle PDV

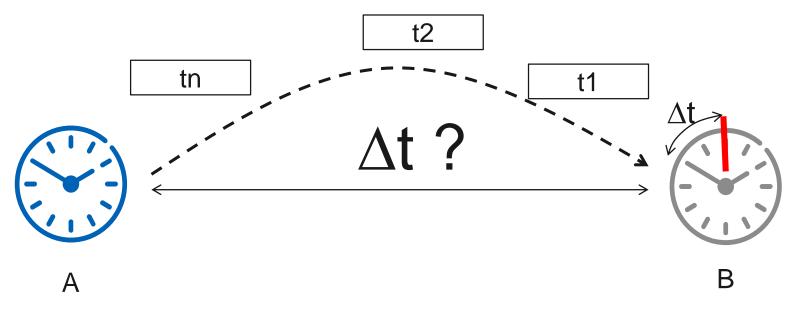

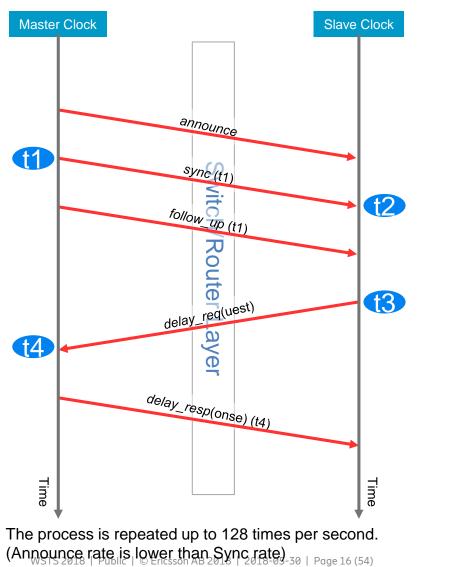

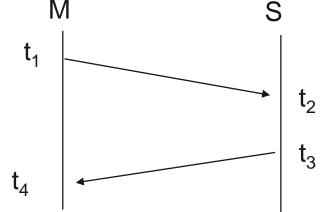

# Two-ways time transfer

Delivery of Time synchronization requires also the knowledge of «transit delay» from A to B

### > **Two-ways transfer protocols** (round trip delay)

- Assumption for symmetric channel

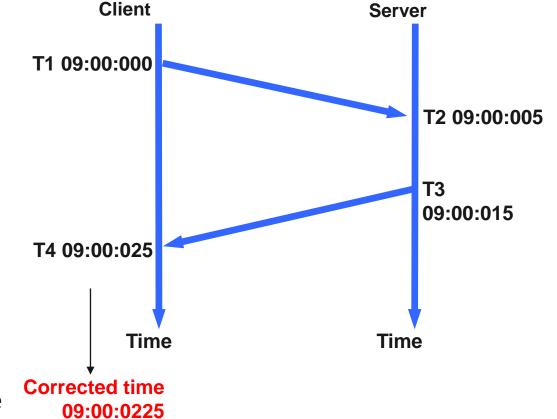

# How NTP Works

- T1 Originate Timestamp

- Time request sent by client

- T2 Receive Timestamp

- Time request received by server

- T3 Transmit Timestamp

- Time reply sent by server

- T4 Destination Timestamp

- Time reply received by client

- Round Trip Delay=(T4-T1)-(T3-T2)

- Round Trip Delay =25-10=15

- Clock Offset= [(T2-T1)-(T4-T3)]/2

- Clock Offset =[5-10]/2= -2.5 (Clients actual time when reply received was therefore 09:00:0225)

- Key Assumptions:

- One way delay is half Round Trip (symmetry!)

- Drift of client and server clocks are small and close to same value

- Time is traceable

# IEEE 1588-2008 (PTPv2)

- The **Grandmaster** "reference clock" sends a series of time-stamped messages to slaves.

- Slaves process the round-trip delay & synchronize to the Grandmaster.

- Frequency can be recovered from an accurate time of day reference (but L1 can also be used ... )

- Best Master Clock Algorithm to define the hierarchy

- Accuracy is possible by means of:

- Proper packet rate (up to 128 per second)

- Hardware time-stamping (eliminate software processing delays)

- Timing support in the network (e.g. transparent clocks, boundary clocks)

Note: IEEE 1588 under revision (planned 2018/2019)

# PTP Time Transfer Technique

| Data At                                 |

|-----------------------------------------|

| Slave Clock                             |

|                                         |

|                                         |

|                                         |

|                                         |

| Loop accord offect                      |

| Leap second offset                      |

|                                         |

| t2 (& t1 for 1-step)                    |

|                                         |

| t1,t2                                   |

|                                         |

| t1, t2, t3                              |

| (,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, ,, |

|                                         |

|                                         |

|                                         |

|                                         |

|                                         |

| t1, t2, t3, t4                          |

| · · ·                                   |

|                                         |

|                                         |

Round Trip Delay RTD = (t2 - t1) + (t4 - t3)

#### Offset: (slave clock error and one-way path delay) Offset<sub>SYNC</sub> = t2 - t1 $Offset_{DELAY\_REQ} = t4 - t3$ We assume path symmetry, therefore One-Way Path Delay = RTD $\div$ 2 Slave Clock Error = $(t2 - t1) - (RTD \div 2)$ Notes: 1. One-way delay cannot be calculated exactly, but there is a bounded error. 2. The protocol transfers TAI (Atomic Time). UTC time is TAI + leap second offset from the announce message.

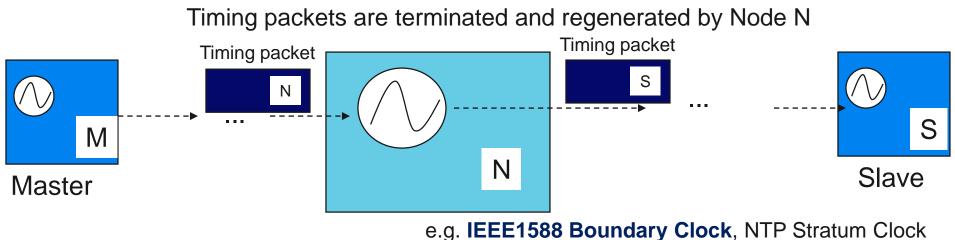

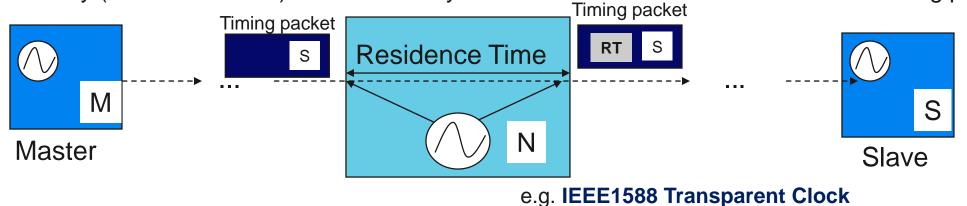

# Timing Support

Latency (Residence Time) is calculated by NE and the information is added in the timing packet

To remove (reduce) «Time Error» components internal to the nodes

# "The Telecom Profile" (G.8265.n/G.8275.n)

- —A profile is a subset of required options, prohibited options, and the ranges and defaults of configurable attributes

- e.g. for Telecom: Update rate, unicast/multicast, etc.

- --PTP profiles are created to allow organizations to specify selections of attribute values and optional features of PTP that, when using the same transport protocol, **inter-works** and achieve a **performance** that meets the requirements of a particular application

- -Other (non-Telecom) profiles:

- IEEE C37.238 (Standard Profile for Use of IEEE 1588 Precision Time Protocol in Power System Applications,)

- IEEE 802.1AS (Timing and Synchronization for Time-Sensitive Applications in Bridged Local Area Networks); Under revision (targeting a full compliance with the next IEEE 1588 revision)

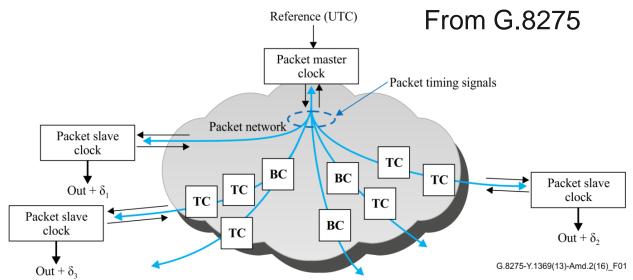

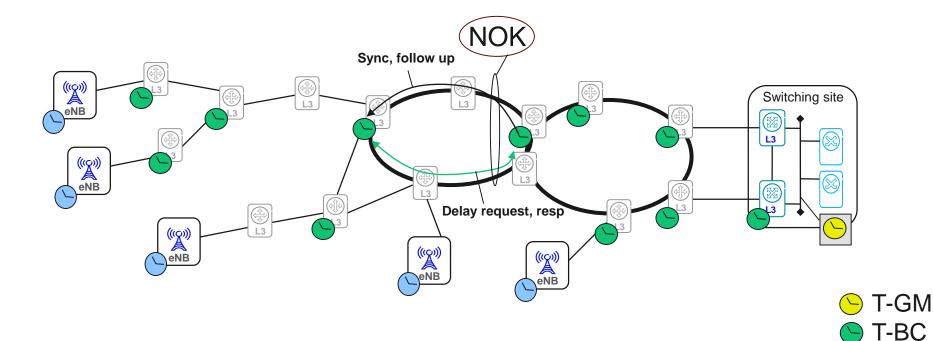

# Time Synchronization Architecture

- General network topology for time/phase distribution from a packet master clock PRTC to a telecom time slave clock (T-TSC)

- > The synchronization flow is from the master to slave, although the timing messages will flow in both directions.

- Individual nodes are T-BCs or T-TCs in the case of full support from the network

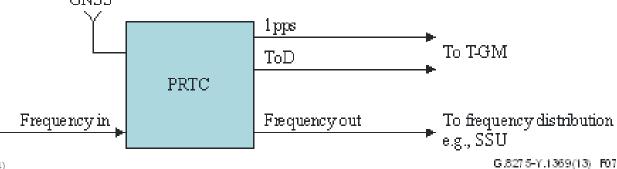

Primary Reference Time Clock (PRTC) is the master of the time synchronization network (G.8272).

ePRTC (enhancedPRTC) recently defined (G.8272.1). Cluster of PRTCs being discussed («cnPRTC» Coherent Network PRTC)

# T-BC and T-TC clock models

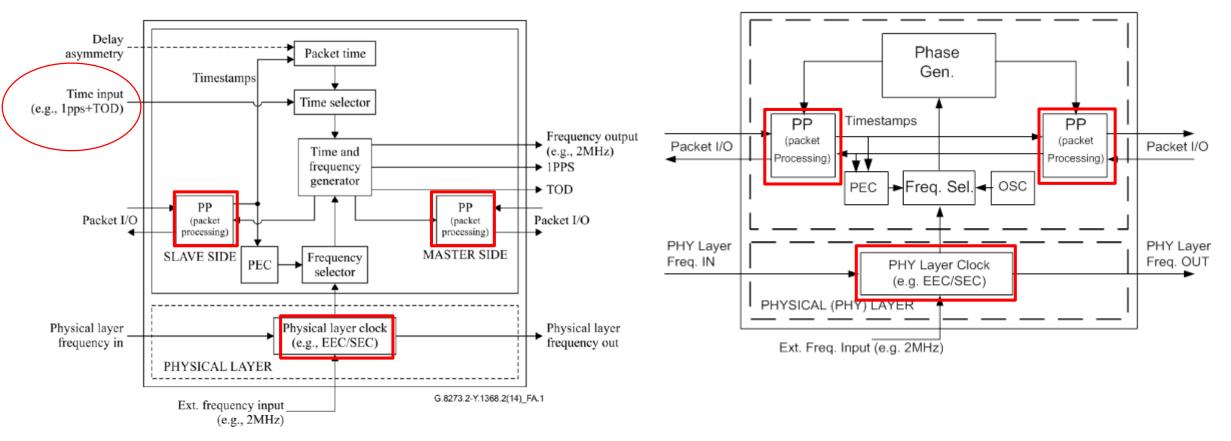

-G.8273.2 and G.8273.3 provide models for the Telecom Boundary and Transparent Clocks

- Frequency sync via physical layer initially considered

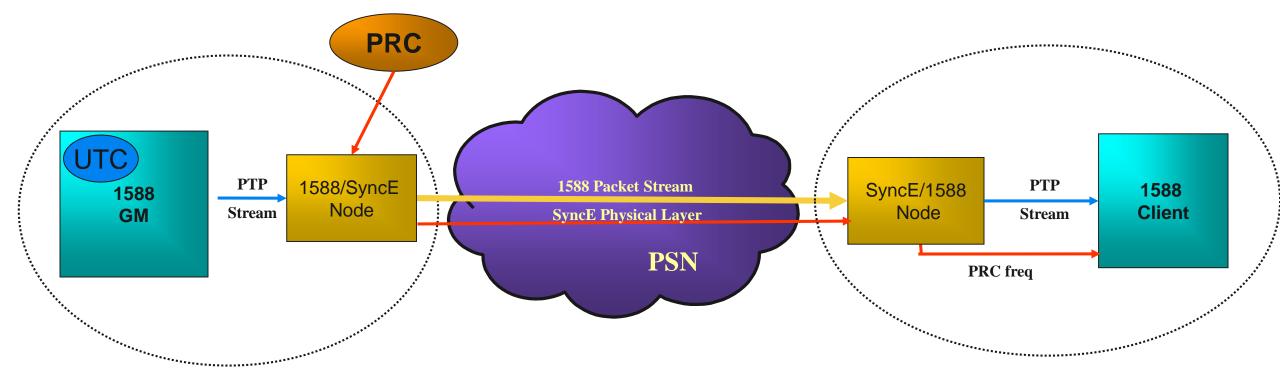

# Combined PTP-SyncE

> SyncE as "frequency assistance" to 1588

- > Gives immediate "frequency lock" to 1588 client

- > SyncE & 1588 functionality may be in the same node/element

- > SyncE might be used for "Time sync holdover"

WSTS 2018 | Public | © Ericsson AB 2018 | 2018-05-30 | Page 21 (54)

# Impairments in Packet networks

- —Physical path asymmetry

- —Path rerouting

- —Packet delay variations [PDV], depending on

- Network dimension

- Traffic load

- QoS

- -Interactions between the packet streams

# Time Synchronization via PTP: Asymmetry related impairments

—Basic principle: distribute Time sync reference by means of two-way time stamps exchange

Time Offset=  $t_2 - t_1$  – Mean path delay Mean path delay = (( $t_2 - t_1$ ) + ( $t_4 - t_3$ )/2

- —As for NTP, also in case of PTP, symmetric paths are required:

- Basic assumption:  $t_2 t_1 = t_4 t_3$

- Any asymmetry will contribute with half of that to the error in the time offset calculation (e.g. 3  $\mu$ s asymmetry would exceed the target requirement of 1.5  $\mu$ s)

### Asymmetry In Transport Networks

### -Different paths in Packet networks

- Traffic Engineering rules in order to define always the same path for the forward and reverse directions

- —Different Fiber Lengths in the forward and reverse direction

- Additional problem: DCF (Dispersion Compensated Fiber)

- —Different Wavelengths used on the forward and reverse direction

- —Asymmetries added by specific access and transport technologies

- GPON

- VDSL2

- Microwave

- OTN

### Path Asymmetry and Rerouting

- -Asymmetry

- Static difference in paths between the forward and reverse paths

- Forward and reverse paths pass through different nodes

### -Rerouting

- Leads change in path delays and can "confuse" the algorithms.

T-TSC

### PDV: a Key Aspect in Packet Timing Performance

- Packet Delay Variation (PDV) is a major contributor to "clock noise"

- Related to number of hops, congestion, line-bit-rate, queuing priority, etc. Timestamp-error can be viewed as part of PDV

- Clock recovery involves low-pass-filter action on PDV

- Oscillator characteristics determine degree of filtering capability (i.e. tolerance to PDV)

- Higher performance oscillators allow for longer time-constants (i.e. stronger filtering)

- Lower performance (less expensive) oscillators may be used (may require algorithmic performance improvements)

- Performance improvements can be achieved by

- Higher packet rate

- Controlling PDV in network (e.g. network engineering, QoS)

- Timing support from network (e.g. *boundary clocks* in PTP)

- Packet selection and/or nonlinear processing

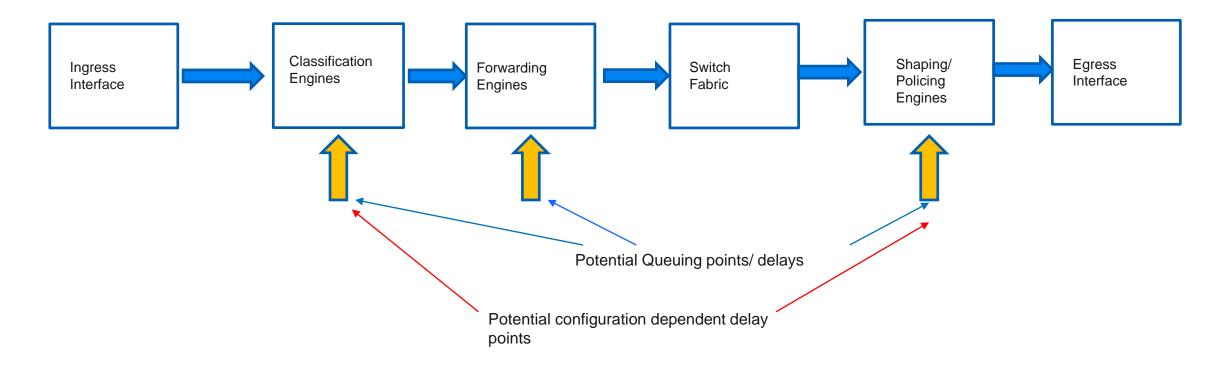

# Packet delay variation (PDV)

- Queuing

- Equipment Configuration

- Priority/ QoS

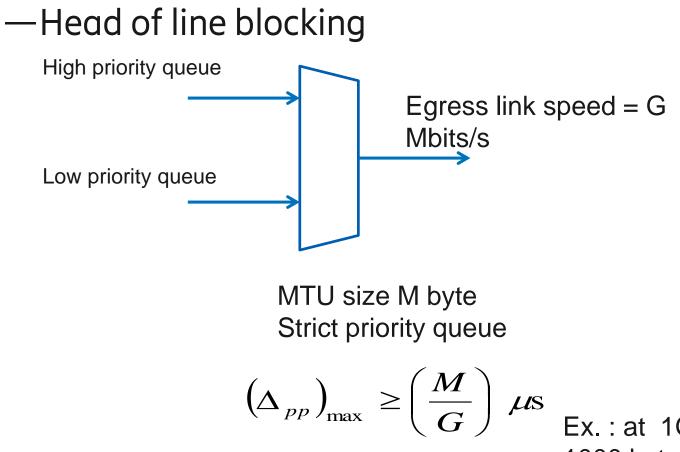

# Packet delay variation (PDV), Cont.

- A packet arrives in the HPQ, just when a packet from the LPQ has begun transmission

- The packet from HPQ is blocked till the LPQ packet is transmitted

- With more complex prioritization scheme the delay due to head of line blocking could vary significantly

- Tools specified by IEEE 802.1 to address this issue (e.g. frame preemption, scheduled traffic)

Ex. : at 1Gbit/s, 1000 byte packet = 8 x 1000 / 1000 x  $10^6 = 8 \mu s$

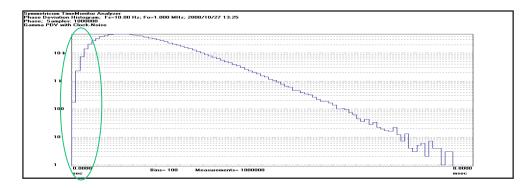

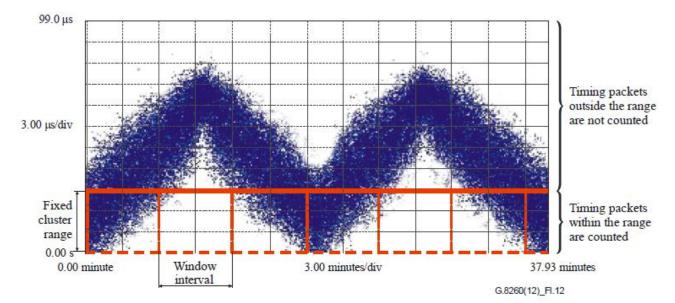

# Notion of "Best Packets"

- Impact of PDV can be mitigated by means of a suitable classification and **selection** of packets

- The "minimum delay" approach is an example. Depending on the network characteristics other approaches may be more suitable

- The assumption that the path is constant over the interval of observation implies a PDV with a distribution function with a slowly changing floor (i.e. minimum delay that a packet can experience)

- In many cases it has been observed that a reasonable fraction (e.g. x%) of the total number of packets will traverse the network at or near this floor

- Using only these packets in the timing recovery mechanism would allow to significantly reduce the impact

of the PDV on the quality of the recovered reference timing signal

# Sync Metrics in Packet Networks

- The Network Element clock output metrics as per TDM networks (e.g. MTIE/MRTIE/TDEV)

- Some distinctions are required in case of packet clock integrated in the Base Station (no standardized output MTIE/TDEV by 3GPP)

- Specific Metrics have been defined to better characterize the behavior of packet networks (PDV) delivering the timing reference

- Metrics that associate PDV with Frequency Offset or phase variation

- Tolerance masks/Network limits are used by network operators and clock manufacturers

- Packet selection methods can be justified

[Clock stability quantities estimation] = function (PDV stability quantities) G.8260(10)\_F1.1

# Floor Packet Percentage

Family of metrics based on counting amount of packets, observed for any window interval of t seconds within a fixed cluster range starting at the observed floor delay and having a size δ

- Floor Packet Percent (FPP) defined in terms of percentage of packets meeting these criteria

- > Basis for the G.8261.1 network limits (150 / 75 us)

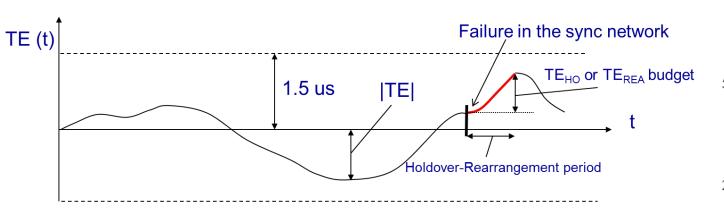

# Time Sync performance metric: Full Timing Support

- Max abs(TE) for combined **dynamic** and **constant time error**

- MTIE (low frequency) and «peak-to-peak TE amplitude» (high frequency) for dynamic time error

$TE_{\rm HO}$  applicable to the network (End Application continues to be locked to the external reference)  $TE_{\rm REA}$  applicable to the End Application (End Application handles short rearrangement periods)

# Time Sync performance metric: Partial Timing Support

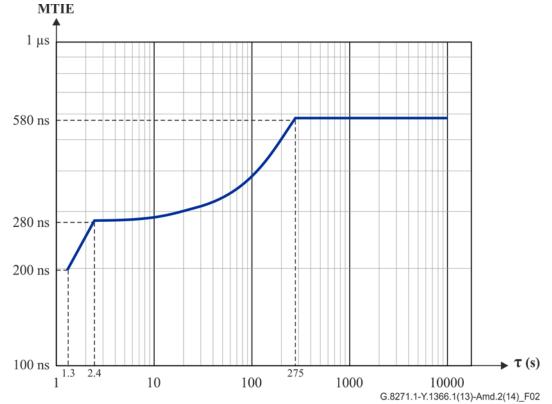

- Metric : «Packet selected 2WayTE»

- APTS, Assisted Partial Timing Support: **Peak-to-peak pktSelected2WayTE**

- PTS: max |pktSelected2WayTE|

+/-100ns

T-GM

PRTC,

PRC

#### — Network Limit (G.82/1.2):

- 1.35µs in terms of maximum absolute time error (at the output of the clock); if GNSS is lost.

- 1.1 µs at the input of the T-TSC

- 2 classes of network limits addressing different end applications cases, distinguished by different Packet Selection criteria

- High Stability Clocks: window interval of 200s percentage of 0.25%

- Low stability clocks, under study

Note: G.8273.4 under development (clock for PTS and APTS)

Packet

Network

R

+/-1100ns

T-BC-P

Packet

Network

PRTC/

GNSS

T-TSC-A

GNSS-assisted

n

+/-1350ns

Master

R

Probe

+/-1500ns

End Application

Distributed Arch (e.g. CPRI)

- Packet Timing in ITU-T: ITU-T G.826x series, G.827x series,

- ITU-T general definitions: G.810, G.8260

- NTP: IETF RFC 5905/6/7/8

- PTP: IEEE 1588-2008

- CES: RFC 5087, RFC 5086, RFC4533, ITU-T Y.1413, ITU-T Y.1453, MEF3, MEF 8

Ericsson.com